# ARICH

# Ultrashort Channel Length Black Phosphorus Field-Effect Transistors

Jinshui Miao, Suoming Zhang, Le Cai, Martin Scherr, and Chuan Wang\*

Electrical and Computer Engineering, Michigan State University, East Lansing, Michigan 48824, United States

**ABSTRACT** This paper reports high-performance top-gated black phosphorus (BP) field-effect transistors with channel lengths down to 20 nm fabricated using a facile angle evaporation process. By controlling the evaporation angle, the channel length of the transistors can be reproducibly controlled to be anywhere between 20 and 70 nm. The as-fabricated 20 nm top-gated BP transistors exhibit respectable on-state current ( $174 \, \mu A/\mu m$ ) and transconduc-

tance (70  $\mu$ S/ $\mu$ m) at a V<sub>DS</sub> of 0.1 V. Due to the use of two-dimensional BP as the channel material, the transistors exhibit relatively small short channel effects, preserving a decent on—off current ratio of 10<sup>2</sup> even at an extremely small channel length of 20 nm. Additionally, unlike the unencapsulated BP devices, which are known to be chemically unstable in ambient conditions, the top-gated BP transistors passivated by the Al<sub>2</sub>O<sub>3</sub> gate dielectric layer remain stable without noticeable degradation in device performance after being stored in ambient conditions for more than 1 week. This work demonstrates the great promise of atomically thin BP for applications in ultimately scaled transistors.

KEYWORDS: black phosphorus · 2D semiconductors · field-effect transistors · device scaling · ultrashort channel length

s the scaling of the silicon-based transistor approaches its physical limit, exploratory research is needed to develop alternative channel materials for future sub-5 nm gate length devices. For such an ultrascaled electronic device, short channel effects would severely limit its performance and operation.<sup>1</sup> In order to suppress the short channel effects at extreme scaling limits, the thickness of the channel material needs to be less than roughly onethird of the gate length in order to allow the gate to retain its effective electrostatic control of channel carrier concentration.<sup>2,3</sup> However, for conventional semiconductors, the rough surface of the ultrathin body (a few atomic layers) would lead to severe surface scattering for carriers, resulting in severely degraded carrier mobility.<sup>4,5</sup> In this regard, two-dimensional (2D) lavered semiconductors are excellent candidates for future ultimately scaled electronic devices because they are atomically smooth and free of dangling bonds/defect states, which lead to intrinsically low surface scattering.<sup>6</sup> Another important advantage of these atomically thin 2D semiconductors is their immunity to short channel effects due to their small thickness.<sup>7</sup> Current research in 2D layered materials

primarily focuses on graphene,<sup>8-12</sup> insulating hexagonal boron nitride,<sup>13</sup> and transition metal dichalcogenides (TMDCs),<sup>14</sup> such as tungsten diselenide (WSe<sub>2</sub>)<sup>4,15</sup> and molybdenum disulfide  $(MoS_2)$ .<sup>6,7,16–22</sup> As the most extensively studied 2D layered material, graphene possesses superior carrier mobility up to  $10^5$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, but the zero band gap nature poses limitations on its applications in electronic or optoelectronic devices as graphene transistors have a very small amount of gate modulation.<sup>23</sup> Transistors made from monolayer or few-layer TMDCs, such as MoS<sub>2</sub> and WSe<sub>2</sub>, exhibit decent on/off current ratios due to their decent band gap size and excellent current saturation characteristics.<sup>24</sup> However, the carrier mobility in TMDCs is much lower than that in graphene and varies largely from 10 to 200 cm<sup>2</sup>  $V^{-1}$  s<sup>-1.6,7</sup>. Recently, a novel elemental 2D material was isolated by mechanical exfoliation of black phosphorus (BP) crystals, an allotrope of the element phosphorus with layered structure.<sup>25–36</sup> Unlike semimetallic graphene, BP is a direct band gap semiconductor with a thickness-dependent band gap ranging from  $\sim$ 0.3 eV (bulk) to  $\sim$ 2.0 eV (monolayer).<sup>37,38</sup> Few-layer BP nanoflakes have been used as channel materials in field-effect transistors

\* Address correspondence to cwang@msu.edu.

Received for review July 1, 2015 and accepted August 16, 2015.

Published online August 17, 2015 10.1021/acsnano.5b04036

© 2015 American Chemical Society

VOL.9 • NO.9 • 9236-9243 • 2015

9236

(FETs). Such BP FETs exhibit high on/off current ratios of  $10^4 - 10^5$  and room temperature field-effect mobility up to  $1000 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ .<sup>37,39,40</sup> These desirable properties make 2D layered BP a promising candidate for high-performance electronic and optoelectronic devices, such as radio frequency transistors,<sup>41</sup> photodetectors, <sup>42–46</sup> memory devices,<sup>47</sup> and digital inverters.<sup>48</sup>

To the best of our knowledge, the smallest BP transistor demonstrated so far has a channel length of approximately 100 nm fabricated by electron beam lithography (EBL).<sup>49</sup> It gets significantly more challenging to further scale down the channel length to below 100 nm due to the limitations in the EBL process, e-beam resist, and lift-off process used. In this paper, we report a novel and facile process combining EBL and angle deposition<sup>50</sup> to fabricate top-gated BP transistors with channel lengths down to 20 nm. With the high-quality few-layer BP obtained from mechanical exfoliation and ultrashort channel length, such devices exhibit respectable on-current and transconductance up to 174  $\mu$ A/ $\mu$ m and 70  $\mu$ S/ $\mu$ m, respectively, at a small drain-to-source voltage of 100 mV. Additionally, although a certain amount of short channel effects are observed at a channel length of 20 nm, the transistors still manage to retain a decent on/off ratio of  $\sim 10^2$ ,

which is expected with the use of ultrathin 2D semiconductor channel material. The results demonstrate the potential of few-layer BP for ultimately scaled transistors.

# **RESULTS AND DISCUSSION**

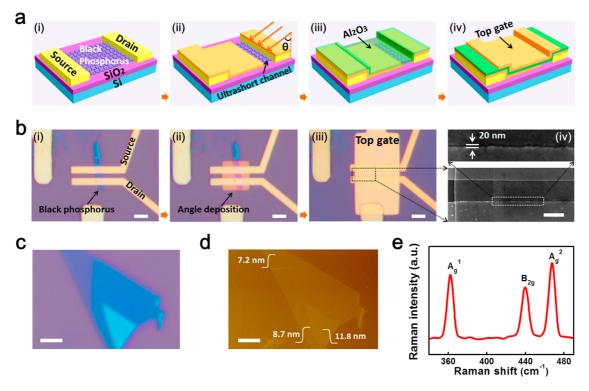

The fabrication process used to obtain the ultrashort channel length BP FETs is illustrated in Figure 1a. More details can be found in the Methods section. Briefly, few-layer BP nanoflakes (<10 nm) were mechanically exfoliated from bulk BP crystals and transferred onto a silicon wafer with 300 nm thick SiO<sub>2</sub>. "Long" channel ( $L \approx 1 \,\mu$ m) BP FETs with 50 nm thick gold (Au) source/ drain (S/D) contacts were then fabricated by EBL patterning, metal evaporation, and lift-off processes (Figure 1a(i), b(i)). A second EBL step was carried out to open a window across the channel region of these "long" channel BP transistors, followed by deposition of 20 nm thick Au film intentionally evaporated with an angle (Figure 1a(ii), b(ii)). With the sample placed at an angle ( $\theta$ ) to the metal evaporation direction, the existing 50 nm thick Au electrodes leave a shadow behind for the second metal deposition, allowing ultrasmall gaps (L between 20 and 70 nm) to be obtained in a facile and controllable fashion. Finally, atomic layer

Figure 1. BP FET with a channel length of 20 nm fabricated by angle evaporation. (a) Schematic diagrams illustrating the fabrication process of the ultrashort channel length BP FETs. (i) "Long" channel BP FET obtained directly from EBL patterning and lift-off process; (ii) back-gated ultrashort channel BP FET obtained from angle evaporation; (iii) atomic layer deposition of 10 nm thick  $Al_2O_3$  film as the gate dielectric; (iv) EBL patterning of the top gate for the ultrashort channel BP FET. (b) Optical microscope and SEM images of a representative ultrashort channel length BP FET at various stages of the fabrication process. Optical micrograph of a "long" channel ( $L = 1 \mu m$ ) BP FET (i), a 20 nm back-gated BP FET obtained after the angle evaporation process (ii), and a 20 nm top-gated BP FET (iii). The scale bar for (i–iii) is  $2 \mu m$ . Panel (iv) shows the SEM image of the same device with a 20 nm channel length. Scale bar:  $1 \mu m$ . (c) Optical image of a representative BP nanoflake used in this study. Scale bar:  $2.5 \mu m$ . (d) AFM image of the same BP nanoflake. Scale bar:  $2.5 \mu m$ . (e) Raman spectra of the BP nanoflake used in this study.

VOL.9 • NO.9 • 9236-9243 • 2015 A

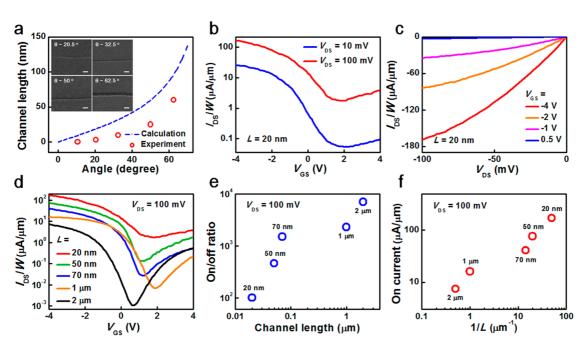

Figure 2. Electrical characteristics of ultrashort channel BP FETs. (a) Device channel length as a function of angle used during the metal deposition. Inset: SEM images of various channel lengths obtained. Scale bar: 50 nm. (b) Transfer characteristics ( $I_{DS}-V_{GS}$ ) of a top-gated BP FET with a channel length of 20 nm. (c) Output characteristics ( $I_{DS}-V_{DS}$ ) of the same device in (b). (d) Comparison of transfer curves for top-gated BP FETs with various channel lengths. (e) Device on/off current ratio plotted as a function of channel length. (f) Device on-current density plotted as a function of 1/L.

deposition (ALD) was used to deposit a 10 nm thick Al<sub>2</sub>O<sub>3</sub> layer as the gate dielectric, followed by a third EBL patterning, metal evaporation, and lift-off process to obtain the top-gate electrode (Figure 1a(iii,iv)). Figure 1b shows the optical and scanning electron microscope (SEM) images of a representative top-gated 20 nm BP FET at various stages of the fabrication process. An ultrashort channel length of around 20 nm is evident from the SEM image in Figure 1b(iv). BP nanoflakes used in this study typically have thickness below 10 nm, and the representative optical micrograph and atomic force microscope (AFM) image are shown in Figure 1c,d, respectively. Figure 1e shows the Raman spectra obtained from the BP flake, in which three peaks can be observed at  $\sim$ 362,  $\sim$ 439, and  $\sim$ 467 cm<sup>-1</sup>, corresponding to the  $A_q^{1}$ ,  $B_{2q}$ , and  $A_q^{2}$  phonon modes for pristine BP materials.40

The electrical characteristics of top-gated BP FETs with various channel lengths are presented in Figure 2. Figure 2a illustrates that the device channel length can be effectively controlled by varying the evaporation angle. The measured channel lengths from SEM (red open circle) agree well with the calculated values (blue dashed line) using the equation  $L = t \times \tan(\theta)$ , where L, t, and  $\theta$  correspond to channel length, first electrode thickness (50 nm in this work), and evaporation angle, respectively. For ultrashort channel FETs, the gate oxide layer needs to be thin enough to allow effective electrostatic control of the channel carrier concentration by the gate electrode.<sup>4</sup> If the gate is not sufficiently strong, then the drain fights with the gate over the channel control, resulting in poor gate dependence.

As shown in Supporting Information Figure S1, the transfer characteristics  $(I_{DS} - V_{GS})$  of a back-gated BP FET with L = 20 nm measured at a drain-to-source voltage ( $V_{DS}$ ) of 1 mV indicates that the back-gate bias cannot fully deplete the channel due to the 300 nm thick SiO<sub>2</sub> dielectric layer used. In this regard, the top gate with an ultrathin dielectric layer is needed for effective gate control. Figure 2b shows the transfer characteristics of a top-gated 20 nm long BP FET with a 10 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric measured at  $V_{DS} = 10$  and 100 mV. The device exhibits a respectable on-current of 174  $\mu$ A/ $\mu$ m and decent on/off ratio of  $10^2$  with  $V_{DS} = 100$  mV. The current increases as the top-gate voltage sweeping from positive to negative, indicating the p-type transistor behavior. Output characteristics  $(I_{DS} - V_{DS})$  of the same device with various top-gate biases (-4, -2, -1, and0.5 V) are shown in Figure 2c. At small  $V_{DS}$  values, the drain current varies linearly with the drain voltage, indicating that the Schottky barrier is low and thin enough to allow Ohmic contact-like behavior between the Au metal and BP. More details about the Schottky barrier and contact resistance will be discussed later.

To assess the performance of the 20 nm top-gated BP FETs fabricated using our angle evaporation approach, the relevant figures-of-merit for recently reported BP-based FETs are summarized and compared in Table 1.<sup>37,38,41,49,51,52</sup> Due to the adoption of the smallest channel length (20 nm), our devices exhibit the highest on-state current (174  $\mu$ A/ $\mu$ m) to date at a small source drain bias of 100 mV. Slightly higher on-current values of 200 or 350  $\mu$ A/ $\mu$ m have been reported,<sup>41,52</sup> albeit at a much higher source drain bias of 2 V. To study

VOL.9 • NO.9 • 9236-9243 • 2015

JAI

www.acsnano.org

TABLE 1. Comparison of On-State Current for BP FETs **Reported in the Literature**

| contact material | channel length                                        | V <sub>DS</sub>                                                                     | on-state current                                                                                                                 |

|------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Au               | 20 nm                                                 | 0.1 V                                                                               | $\sim$ 174 $\mu$ A/ $\mu$ m                                                                                                      |

| Pd/Au            | 100 nm                                                | 0.5 V                                                                               | $\sim$ 100 $\mu$ A/ $\mu$ m                                                                                                      |

| Ti/Pd/Au         | 300 nm                                                | 2 V                                                                                 | $\sim$ 350 $\mu$ A/ $\mu$ m                                                                                                      |

| Ti/Pd/Au         | $1 \mu \mathrm{m}$                                    | 2 V                                                                                 | $\sim$ 200 $\mu$ A/ $\mu$ m                                                                                                      |

| Ti/Au            | 1 <i>μ</i> m                                          | 2 V                                                                                 | $\sim$ 100 $\mu$ A/ $\mu$ m                                                                                                      |

| Ti/Au            | 5 μm                                                  | 0.1 V                                                                               | $\sim$ 1 $\mu$ A/ $\mu$ m                                                                                                        |

| Ni               | 2 μm                                                  | 0.2 V                                                                               | $\sim$ 50 $\mu$ A/ $\mu$ m                                                                                                       |

|                  | Au<br>Pd/Au<br>Ti/Pd/Au<br>Ti/Pd/Au<br>Ti/Au<br>Ti/Au | Au 20 nm   Pd/Au 100 nm   Ti/Pd/Au 300 nm   Ti/Pd/Au 1 μm   Ti/Au 1 μm   Ti/Au 5 μm | Au 20 nm 0.1 V   Pd/Au 100 nm 0.5 V   Ti/Pd/Au 300 nm 2 V   Ti/Pd/Au 1 μm 2 V   Ti/Au 1 μm 2 V   Ti/Au 1 μm 2 V   Ti/Au 1 μm 2 V |

the channel length scaling of BP FETs, the transfer characteristics of five BP FETs with channel lengths of 0.02, 0.05, 0.07, 1, and 2  $\mu$ m measured at  $V_{DS}$  = 100 mV are presented in Figure 2d. The device on/off current ratio (Ion/Ioff) and unit-width-normalized on-current  $(I_{DS}/W)$  are extracted from Figure 2d and plotted as functions of channel length, as shown in Figure 2e,f, respectively. As the channel length aggressively scales from 2  $\mu$ m to 20 nm, the average on/off current ratio decreases from  $\sim 10^4$  to  $\sim 10^2$ , which can be attributed to the drain-induced barrier lowering (DIBL) and thermal-assisted tunneling process.<sup>49</sup> When the device channel length is extremely small, the drain bias will affect the energy barrier at the source side. As a result, the source barrier is now controlled simultaneously by both gate and drain voltages for ultrashort channel length devices, making such devices more difficult to turn off (Figure 2e). The extent of the short channel effects depends on the thickness of the semiconductor body relative to the channel length. The channel length of 20 nm is already approaching the thickness of the BP nanoflakes used in this work (around 10 nm). With such BP transistors exhibiting an on/off ratio of  $\sim 10^2$  at an extremely small channel length of 20 nm, we consider the short channel effects to be relatively small and acceptable. In the future, the use of thinner or even monolayer BP nanoflakes could lead to ultrashort channel length transistors with even better immunity to short channel effects.

For the on-current, it is approximately inversely proportional to the channel length, as shown in Figure 2f, which agrees well with the classical FET theory. It is worth noting that compared with the "long channel" devices (L = 1 and  $2 \mu m$  in Figure 2f), the on-current for "short channel" devices (L = 20, 50, and 70 nm in Figure 2f) is slightly below the predicted values from the linear extrapolation of the "long channel" data points. The reason is that the "long channel" devices were fabricated with a single-step EBL patterning with relatively thick (50 nm) Au S/D electrodes, while the "short channel" devices fabricated from angle evaporation had thinner (20 nm) S/D electrodes. The smaller S/D contact thickness leads to larger S/D series resistance, whose effect may not be significant for long channel devices but could be dominant when the

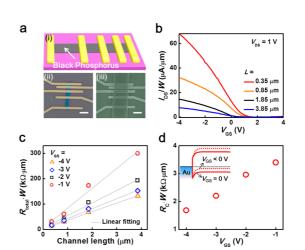

Figure 3. TLM method for extracting the contact resistance of BP FETs. (a) Schematic diagram (i), optical micrograph (ii), and SEM image (iii) showing the TLM structure with topgated BP FETs of various channel lengths (0.35, 0.85, 1.85, and 3.85  $\mu$ m) fabricated on the same BP nanoflake. A 10 nm thick Al<sub>2</sub>O<sub>3</sub> layer is used as the top-gate dielectric in panel (iii). Scale bar: 4  $\mu$ m. (b) Transfer characteristics of the topgated BP FETs in the TLM structure measured at  $V_{DS} = 1$  V. (c) Normalized total resistance  $(R_{total})$  as a function of channel length for various gate biases. (d) Extracted contact resistance  $(R_c)$  as a function of the top-gate voltage. Inset: Energy band diagram of the Au/BP contact.

channel length becomes extremely small. Another possible mechanism that could lead to the slightly lower than predicted on-state current for ultrashort devices is the exposure of BP in ambient conditions, which is known to cause performance degradation in BP FETs.<sup>51</sup> We did our best to prevent the BP degradation during the fabrication from affecting the device performance by always passivating the sample with poly(methyl methacrylate) (PMMA) between the fabrication steps and storing the samples in an argon-filled glovebox when not in use. Nevertheless, the ultrashort channel devices did go through one more step of EBL patterning, metal deposition, and lift-off process before the Al<sub>2</sub>O<sub>3</sub> capping compared with the long channel devices, which could contribute to momentary exposure in ambient conditions and thereby slightly degraded performance.

Contact resistance  $(R_c)$  plays an important role in transistor performance, particularly for those with ultrashort channel lengths.<sup>7,49</sup> Understanding the metal/BP contact is of great scientific and technological importance. The  $R_c$  can be extracted using the transfer length method (TLM) for BP FETs with long channel lengths.<sup>49,53</sup> In this case, the channel length is much larger than the carrier mean free path, and the channel can be considered to be entirely diffusive. A typical backand top-gated BP FET array is presented in Figure 3a, showing four transistors fabricated on the same BP nanoflake used for TLM measurements. Figure 3b shows the transfer characteristics measured at  $V_{DS} = 1$  V for devices with various channel lengths (0.35, 0.85, 1.85, and 3.85  $\mu$ m). The maximum on-current occurs at a

VOL.9 NO.9 9236-9243 2015 AC

top-gate voltage of -4 V. Figure 3c presents the normalized on-state total resistance ( $R_{total}$ ), which includes both the channel resistance and  $R_{cr}$  plotted as a function of channel length. The decrease of R<sub>total</sub> with more negative gate bias is simply due to the increase of carrier concentration in BP FETs. The S/D contact resistance  $(2 \times R_c)$  can be extracted from the y-axis intercepts of the linear fit (light gray line in Figure 3c). The extracted  $R_{\rm c}$ (1688, 2208, 2964, and 3401  $\Omega \cdot \mu m$  at a  $V_{GS}$  of -4, -3, -2, and -1 V, respectively) is then plotted as a function of top-gate voltage in Figure 3d. The  $R_c$  exhibits clear gate dependence and decreases monotonically as the top-gate voltage decreases from -1 to -4 V. This relationship can be explained using the energy band diagram of the metal/p-type BP junction presented as the inset of Figure 3d. A more negative gate bias (dashed line in Figure 3d inset) would result in a narrower Schottky barrier between the Au metal and p-type BP interface, which would facilitate the hole injection from the metal into the valence band of BP, resulting in smaller  $R_c$ .

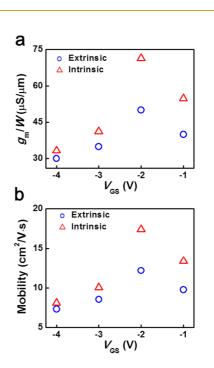

For the long channel devices whose L is much larger than carrier mean-free path, the devices operate entirely in the diffusive regime and the contribution from the  $R_c$  is much smaller compared with the channel resistance. As a result, the R<sub>c</sub> will have little effect on the extracted field-effect mobility. Nevertheless, for ultrashort channel devices, contribution from  $R_c$  becomes dominant and needs to be taken into consideration for precise evaluation of the intrinsic field-effect mobility. In order to do so, the extrinsic transconductance values (blue open circles in Figure 4a) are first extracted by differentiating the transfer curves ( $V_{DS} = 100 \text{ mV}$ ) presented in Figure 2b. The peak extrinsic transconductance of 50  $\mu$ S/ $\mu$ m occurs at V<sub>GS</sub> = -2 V. The intrinsic transconductance  $(g_{mi})$  of the devices can be deduced by excluding the effect of  $R_c$  using the equation  $g_{\rm mi} = g_{\rm m}/(1 - 2g_{\rm m}R_{\rm c})$ . Using the above equation, the peak intrinsic transconductance is found to be 70  $\mu$ S/ $\mu$ m at V<sub>GS</sub> = -2 V, as shown in Figure 4a (red open triangles). Both extrinsic (u) and intrinsic  $(\mu_i)$  field-effect mobilities can then be calculated using the equation  $\mu = L(g_m/W)/(C_{ox}V_{DS})$ , where  $C_{ox}$  is the unit-area capacitance of the 10 nm Al<sub>2</sub>O<sub>3</sub> ( $\varepsilon$  = 9.3) gate dielectric. Using extrinsic (intrinsic)  $g_{\rm m}$  values for the equation would lead to extrinsic (intrinsic) mobility accordingly. For our top-gated BP FETs with 20 nm channel length, the peak extrinsic and intrinsic field-effect mobilities were extracted to be  $\sim$ 12 and  $\sim$ 17 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively, as shown in Figure 4b. It is worth noting that, although mobility values of greater than 100  $\text{cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  have been reported for BP FETs in some other reports cited in the table above, those devices are either long channel or back-gated devices. It is widely known that top-gating causes increased surface scattering due to the addition of the top-gate dielectric layer and short channel length

Figure 4. Extrinsic and intrinsic transconductance and fieldeffect mobility of the ultrashort channel length BP FET. (a) Device transconductance (normalized to the width of the BP nanoflake) at various gate biases measured at a  $V_{DS}$  of 100 mV. (b) Extrinsic and intrinsic field-effect mobility at various gate voltages.

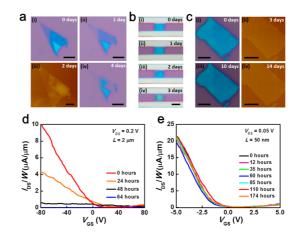

Figure 5. Air stability of back-gated and top-gated BP FETs. (a) Optical micrographs and AFM image of an unencapsulated BP nanoflake right after exfoliation (i) and after being stored in ambient conditions for 1 (ii), 2 (iii), and 4 (iv) days, showing obvious degradation. Scale bar for panels (i,ii,iv): 4  $\mu$ m. Scale bar for panel (iii): 3  $\mu$ m. (b) Optical micrographs of an unencapsulated back-gated BP FET right after fabrication (i) and after being stored in ambient conditions for 1 (ii), 2 (iii), and 3 (iv) days, showing similar degradation. Scale bar: 2  $\mu$ m. (c) Optical micrographs and AFM images of a representative BP nanoflake passivated with 10 nm of Al<sub>2</sub>O<sub>3</sub> right after exfoliation (i) and after being stored in ambient conditions for 3 (ii), 10 (iii), and 14 (iv) days. Scale bars: 2.5 µm. (d) Transfer characteristics of an unencapsulated back-gated BP FET measured after being exposed to ambient conditions for various amounts of time. (e) Transfer characteristics of an ultrashort (L = 50 nm) top-gated BP FET with a 10 nm thick Al<sub>2</sub>O<sub>3</sub> gate dielectric measured after being exposed to ambient conditions for various amounts of time.

www.acsnano.org

leads to carrier velocity saturation, both of which would result in reduced mobility. The mobility values of our top-gated ultrashort channel (L = 20 nm) BP FETs are comparable or slightly higher than those of the previously reported back-gated 100 nm channel length BP FETs whose intrinsic mobility is ~10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1.49</sup>

Pristine BP nanoflakes are known to be chemically unstable upon exposure to ambient conditions because the ambient adsorbates such as moisture irreversibly convert BP into PO<sub>x</sub> compounds, fundamentally altering its electronic and material properties.<sup>51</sup> Figure 5a provides the optical micrographs and AFM image showing the degradation of an unencapsulated BP nanoflake on SiO<sub>2</sub>/Si substrates when stored in ambient conditions. As time goes by, bubbles began to appear on the BP surface (AFM image) and the majority part of the BP flake disappeared after around 4 days. Similar behavior was observed in back-gated BP FETs, as shown in Figure 5b. Specifically, panels i-iv of Figure 5b correspond to the optical micrographs of an as-fabricated back-gated BP FET after being stored in ambient conditions for 0, 1, 2, and 3 days, respectively. Previous reports have shown that BP can be effectively protected from ambient degradation by appropriately chosen passivation layers.<sup>51</sup> Similar to previous reports, we have found that the Al<sub>2</sub>O<sub>3</sub> gate dielectric deposited by ALD serves as an effective passivation layer. As an example, Figure 5c shows the optical micrographs and AFM images of a BP nanoflake passivated by 10 nm thick Al<sub>2</sub>O<sub>3</sub> right

## **METHODS**

Device Fabrication. The few-layer BP nanoflakes were mechanically exfoliated from bulk single crystals (Smart-element, Austria) and then transferred onto a heavily doped silicon substrate with a 300 nm thick SiO<sub>2</sub> dielectric layer. Prior to device fabrication, the substrate with BP nanoflakes was soaked in acetone for 1 h to remove the tape residues. Bilayer PMMA e-beam resists (MicroChem 495 A6 and 950 C2) were spincoated (5000 rpm) onto the SiO<sub>2</sub>/Si substrate followed by baking on a hot plate at 175 °C for 5 min. EBL (JEOL 840 with NPGS) was used to define the source/drain patterns, and 50 nm thick Au film was deposited using a thermal evaporator (Edward Auto 306) followed by lift-off process to form the S/D electrodes. The vacuum during evaporation was around 6  $\times$  10<sup>-7</sup> Torr. To achieve ultrashort channel length, a second EBL was carried out to open a window in the same bilayer PMMA resist across the channel region of the long channel BP transistors obtained in the previous step. The 20 nm thick Au film was subsequently evaporated intentionally at an angle ( $\theta$ ), allowing the existing 50 nm thick Au electrode to leave a shadow behind for the second metal deposition. This is done through the use of a tilting/rotating sample holder in the evaporator, allowing the metal evaporation angle to be precisely controlled from 0 to 90°. Additionally, it is necessary to ensure that the sample is always mounted at the same location on the sample holder in order to eliminate even the slightest possibility of variation in the deposition angle. This step forms ultrasmall gaps (L between 20 and 70 nm) between the S/D contacts. Atomic layer deposition (precursor: trimethylaluminum (TMA) and water; deposition temperature = 250 °C) was used to deposit a 10 nm thick Al<sub>2</sub>O<sub>3</sub> layer as the gate dielectric. Finally, a third EBL patterning, gold evaporation, and lift-off were used to define the top-gate electrode.

after exfoliation. Compared with Figure 5a,b, no obvious degradation was observed on the encapsulated BP nanoflake after being stored for 14 days in ambient conditions. Figure 5d,e further compares the effect of Al<sub>2</sub>O<sub>3</sub> passivating on the electrical characteristics of BP FETs. After fabrication and initial measurement (Figure 5d, red line), a back-gated BP FET ( $L = 2 \mu m$ ) was exposed in ambient conditions. Within 64 h of exposure, the device on-current fell drastically from  $\sim$ 10 to  $\sim$ 0.2 nA/ $\mu$ m at a V<sub>DS</sub> of 0.2 V, indicating severe degradation in BP. In contrast, for the top-gated ultrashort channel (L = 50 nm) BP FET, with the passivation from the 10 nm thick Al<sub>2</sub>O<sub>3</sub> gate dielectric layer, no noticeable change was observed in the transfer characteristics even after the device was stored under identical ambient conditions for more than 1 week (174 h).

### CONCLUSIONS

In summary, we report a facile method combining EBL and angle deposition to fabricate high-performance top-gated BP FETs with channel lengths down to 20 nm. With such small channel length, the devices exhibit one of the highest on-current ( $174 \,\mu A/\mu m$  for  $V_{DS} = 100 \text{ mV}$ ) to date for BP transistors. In addition, such ultrascaled BP transistors still preserve decent on/off current ratio (>10<sup>2</sup>) and field-effect mobility (~17 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), which demonstrates the great potential of using BP for future high-performance ultimately scaled electronic and optoelectronic devices.

**Electrical Measurements.** The electrical characteristics of the ultrashort channel length top-gated BP field-effect transistors were measured using a Signatone probe station and an Agilent B1500A semiconductor parameter analyzer. All measurements were conducted in ambient conditions.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This work was funded by Michigan State University. The device fabrication was done in the Keck Microfabrication Facility (KMF) of Michigan State University. The authors would like to thank Dr. Baokang Bi for helpful discussions regarding the fabrication process.

Supporting Information Available: The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsnano.5b04036.

Transfer characteristics of back-gated BP FETs with a channel length of 20 nm (S1) (PDF)

### **REFERENCES AND NOTES**

- Taur, Y. CMOS Design near the Limit of Scaling. *IBM J. Res.* Dev. 2002, 46, 213–222.

- Chau, R.; Kavalieros, J.; Doyle, B.; Murthy, A.; Paulsen, N.; Lionberger, D.; Barlage, D.; Arghavani, R.; Roberds, B.; Doczy, M. In a 50 nm Depleted-Substrate CMOS Transistor (DST). *IEDM Technol. Dig.* 2001, 621–624.

- Luisier, M.; Lundstrom, M.; Antoniadis, D. A.; Bokor, J. Ultimate Device Scaling: Intrinsic Performance Comparisons of Carbon-Based, InGaAs, and Si Field-Effect Transistors for 5 nm Gate Length. *IEDM Technol. Dig.* 2011, 251–254.

VOL.9 • NO.9 • 9236-9243 • 2015 A

- 4. Fang, H.; Chuang, S.; Chang, T. C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792.

- Ko, H.; Takei, K.; Kapadia, R.; Chuang, S.; Fang, H.; Leu, P. W.; Ganapathi, K.; Plis, E.; Kim, H. S.; Chen, S.-Y.; et al. Ultrathin Compound Semiconductor on Insulator Layers for High-Performance Nanoscale Transistors. *Nature* 2010, 468, 286–289.

- Radisavljevic, B.; Radenovic, A.; Brivio, J.; Giacometti, V.; Kis, A. Single-Layer MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* 2011, 6, 147–150.

- Liu, H.; Neal, A. T.; Ye, P. D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 2012, 6, 8563–8569.

- Novoselov, K. S.; Geim, A. K.; Morozov, S. V.; Jiang, D.; Zhang, Y.; Dubonos, S. V.; Grigorieva, I. V.; Firsov, A. A. Electric Field Effect in Atomically Thin Carbon Films. *Science* 2004, *306*, 666–669.

- Zhang, Y.; Tan, Y. W.; Stormer, H. L.; Kim, P. Experimental Observation of the Quantum Hall Effect and Berry's Phase in Graphene. *Nature* **2005**, *438*, 201–204.

- Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E. Large-Area Synthesis of High-Quality and Uniform Graphene Films on Copper Foils. *Science* **2009**, *324*, 1312–1314.

- Liao, L.; Lin, Y.-C.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K. L.; Huang, Y.; Duan, X. High-Speed Graphene Transistors with a Self-Aligned Nanowire Gate. *Nature* **2010**, *467*, 305–308.

- Wu, Y.; Lin, Y. M.; Bol, A. A.; Jenkins, K. A.; Xia, F.; Farmer, D. B.; Zhu, Y.; Avouris, P. High-Frequency, Scaled Graphene Transistors on Diamond-Like Carbon. *Nature* **2011**, *472*, 74–78.

- Song, L.; Ci, L.; Lu, H.; Sorokin, P. B.; Jin, C.; Ni, J.; Kvashnin, A. G.; Kvashnin, D. G.; Lou, J.; Yakobson, B. I. Large Scale Growth and Characterization of Atomic Hexagonal Boron Nitride Layers. *Nano Lett.* **2010**, *10*, 3209–3215.

- Jariwala, D.; Sangwan, V. K.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Emerging Device Applications for Semiconducting Two-Dimensional Transition Metal Dichalcogenides. ACS Nano 2014, 8, 1102–1120.

- Chuang, H.-J.; Tan, X.; Ghimire, N. J.; Perera, M. M.; Chamlagain, B.; Cheng, M. M.-C.; Yan, J.; Mandrus, D.; Tománek, D.; Zhou, Z. High Mobility WSe<sub>2</sub> p-and n-Type Field-Effect Transistors Contacted by Highly Doped Graphene for Low-Resistance Contacts. *Nano Lett.* **2014**, *14*, 3594–3601.

- Kwon, J.; Hong, Y. K.; Han, G.; Omkaram, I.; Choi, W.; Kim, S.; Yoon, Y. Giant Photoamplification in Indirect-Bandgap Multilayer MoS<sub>2</sub> Phototransistors with Local Bottom-Gate Structures. *Adv. Mater.* **2015**, *27*, 2224–2230.

- Yang, L.; Zhong, D.; Zhang, J.; Yan, Z.; Ge, S.; Du, P.; Jiang, J.; Sun, D.; Wu, X.; Fan, Z. Optical Properties of Metal-Molybdenum Disulfide Hybrid Nanosheets and Their Application for Enhanced Photocatalytic Hydrogen Evolution. ACS Nano 2014, 8, 6979–6985.

- Zhang, K.; Hu, S.; Zhang, Y.; Zhang, T.; Zhou, X.; Sun, Y.; Li, T.-X.; Fan, H. J.; Shen, G.; Chen, X. Self-Induced Uniaxial Strain in MoS<sub>2</sub> Monolayers with Local van der Waals-Stacked Interlayer Interactions. ACS Nano 2015, 9, 2704–2710.

- Bao, W.; Cai, X.; Kim, D.; Sridhara, K.; Fuhrer, M. S. High Mobility Ambipolar MoS<sub>2</sub> Field-Effect Transistors: Substrate and Dielectric Effects. *Appl. Phys. Lett.* **2013**, *102*, 042104.

- Das, S.; Chen, H. Y.; Penumatcha, A. V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105.

- Liu, H.; Si, M.; Deng, Y.; Neal, A. T.; Du, Y.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Ye, P. D. Switching Mechanism in Single-Layer Molybdenum Disulfide Transistors: An Insight into Current Flow across Schottky Barriers. ACS Nano 2014, 8, 1031–1038.

- Liu, H.; Si, M.; Najmaei, S.; Neal, A. T.; Du, Y.; Ajayan, P. M.; Lou, J.; Ye, P. D. Statistical Study of Deep Submicron Dual-Gated Field-Effect Transistors on Monolayer Chemical Vapor Deposition Molybdenum Disulfide Films. *Nano Lett.* 2013, 13, 2640–2646.

- Zhang, Y.; Tang, T. T.; Girit, C.; Hao, Z.; Martin, M. C.; Zettl, A.; Crommie, M. F.; Shen, Y. R.; Wang, F. Direct Observation of a Widely Tunable Bandgap in Bilayer Graphene. *Nature* 2009, 459, 820–823.

- Yoon, Y.; Ganapathi, K.; Salahuddin, S. How Good Can Monolayer MoS<sub>2</sub> Transistors Be? *Nano Lett.* 2011, *11*, 3768– 3773.

- Avsar, A.; Vera-Marun, I. J.; Tan, J. Y.; Watanabe, K.; Taniguchi, T.; Castro Neto, A. H.; Özyilmaz, B. Air Stable Transport in Graphene Contacted, Fully Encapsulated Ultra Thin Black Phosphorus-Based Field-Effect Transistors. ACS Nano 2015, 9, 4138–4145.

- Saito, Y.; Iwasa, Y. Ambipolar Insulator-to-Metal Transition in Black Phosphorus by Ionic-Liquid Gating. ACS Nano 2015, 9, 3192–3198.

- Deng, Y.; Luo, Z.; Conrad, N. J.; Liu, H.; Gong, Y.; Najmaei, S.; Ajayan, P. M.; Lou, J.; Xu, X.; Ye, P. D. Black Phosphorus-Monolayer MoS<sub>2</sub> van der Waals Heterojunction p-n Diode. *ACS Nano* **2014**, *8*, 8292–8299.

- Koenig, S. P.; Doganov, R. A.; Schmidt, H.; Castro Neto, A. H.; Özyilmaz, B. Electric Field Effect in Ultrathin Black Phosphorus. *Appl. Phys. Lett.* **2014**, *104*, 103106.

- Na, J.; Lee, Y. T.; Lim, J. A.; Hwang, D. K.; Kim, G.-T.; Choi, W. K.; Song, Y.-W. Few-Layer Black Phosphorus Field-Effect Transistors with Reduced Current Fluctuation. ACS Nano 2014, 8, 11753–11762.

- Qiao, J.; Kong, X.; Hu, Z. X.; Yang, F.; Ji, W. High-Mobility Transport Anisotropy and Linear Dichroism in Few-Layer Black Phosphorus. *Nat. Commun.* 2014, *5*, 4475.

- Yasaei, P.; Kumar, B.; Foroozan, T.; Wang, C.; Asadi, M.; Tuschel, D.; Indacochea, J. E.; Klie, R. F.; Salehi-Khojin, A. High-Quality Black Phosphorus Atomic Layers by Liquid-Phase Exfoliation. *Adv. Mater.* **2015**, *27*, 1887–1892.

- Liu, X.; Wood, J. D.; Chen, K.-S.; Cho, E.; Hersam, M. C. In Situ Thermal Decomposition of Exfoliated Two-Dimensional Black Phosphorus. J. Phys. Chem. Lett. 2015, 6, 773–778.

- Ling, X.; Wang, H.; Huang, S.; Xia, F.; Dresselhaus, M. S. The Renaissance of Black Phosphorus. *Proc. Natl. Acad. Sci. U. S. A.* 2015, *112*, 4523–4530.

- Kang, J.; Wood, J. D.; Wells, S. A.; Lee, J.-H.; Liu, X.; Chen, K.-S.; Hersam, M. C. Solvent Exfoliation of Electronic-Grade, Two-Dimensional Black Phosphorus. ACS Nano 2015, 9, 3596–3604.

- Xiang, D.; Han, C.; Wu, J.; Zhong, S.; Liu, Y.; Lin, J.; Zhang, X.-A.; Hu, W. P.; Özyilmaz, B.; Neto, A. C. Surface Transfer Doping Induced Effective Modulation on Ambipolar Characteristics of Few-Layer Black Phosphorus. *Nat. Commun.* 2015, *6*, 6485.

- Ribeiro, H. B.; Pimenta, M. A.; de Matos, C. J.; Moreira, R. L.; Rodin, A. S.; Zapata, J. D.; de Souza, E. A.; Castro Neto, A. H. Unusual Angular Dependence of the Raman Response in Black Phosphorus. ACS Nano 2015, 9, 4270–4276.

- Li, L.; Yu, Y.; Ye, G. J.; Ge, Q.; Ou, X.; Wu, H.; Feng, D.; Chen, X. H.; Zhang, Y. Black Phosphorus Field-Effect Transistors. *Nat. Nanotechnol.* **2014**, *9*, 372–377.

- Das, S.; Zhang, W.; Demarteau, M.; Hoffmann, A.; Dubey, M.; Roelofs, A. Tunable Transport Gap in Phosphorene. *Nano Lett.* 2014, 14, 5733–5739.

- Kamalakar, M. V.; Madhushankar, B.; Dankert, A.; Dash, S. P. Low Schottky Barrier Black Phosphorus Field-Effect Devices with Ferromagnetic Tunnel Contacts. *Small* 2015, *11*, 2209–2216.

- Liu, H.; Neal, A. T.; Zhu, Z.; Luo, Z.; Xu, X.; Tománek, D.; Ye, P. D. Phosphorene: An Unexplored 2D Semiconductor with a High Hole Mobility. ACS Nano 2014, 8, 4033–4041.

- Wang, H.; Wang, X.; Xia, F.; Wang, L.; Jiang, H.; Xia, Q.; Chin, M. L.; Dubey, M.; Han, S. J. Black Phosphorus Radio-Frequency Transistors. *Nano Lett.* **2014**, *14*, 6424–6429.

- Engel, M.; Steiner, M.; Avouris, P. Black Phosphorus Photodetector for Multispectral, High-Resolution Imaging. *Nano Lett.* 2014, 14, 6414–6417.

- Buscema, M.; Groenendijk, D. J.; Blanter, S. I.; Steele, G. A.; van der Zant, H. S.; Castellanos-Gomez, A. Fast and Broadband Photoresponse of Few-Layer Black Phosphorus Field-Effect Transistors. *Nano Lett.* **2014**, *14*, 3347–3352.

- Buscema, M.; Groenendijk, D. J.; Steele, G. A.; van der Zant, H. S.; Castellanos-Gomez, A. Photovoltaic Effect in Few-Layer Black Phosphorus PN Junctions Defined by Local Electrostatic Gating. *Nat. Commun.* **2014**, *5*, 4651.

- Hong, T.; Chamlagain, B.; Lin, W.; Chuang, H. J.; Pan, M.; Zhou, Z.; Xu, Y. Q. Polarized Photocurrent Response in Black Phosphorus Field-Effect Transistors. *Nanoscale* 2014, 6, 8978–8983.

- Youngblood, N.; Chen, C.; Koester, S. J.; Li, M. Waveguide-Integrated Black Phosphorus Photodetector with High Responsivity and Low Dark Current. *Nat. Photonics* 2015, 9, 247–252.

- 47. Zhang, X.; Xie, H.; Liu, Z.; Tan, C.; Luo, Z.; Li, H.; Lin, J.; Sun, L.; Chen, W.; Xu, Z.; et al. Black Phosphorus Quantum Dots. *Angew. Chem., Int. Ed.* **2015**, *54*, 3653–3657.

- Zhu, W.; Yogeesh, M. N.; Yang, S.; Aldave, S. H.; Kim, J. S.; Sonde, S.; Tao, L.; Lu, N.; Akinwande, D. Flexible Black Phosphorus Ambipolar Transistors, Circuits and Am Demodulator. *Nano Lett.* **2015**, *15*, 1883–1890.

- Du, Y.; Liu, H.; Deng, Y.; Ye, P. D. Device Perspective for Black Phosphorus Field-Effect Transistors: Contact Resistance, Ambipolar Behavior, and Scaling. ACS Nano 2014, 8, 10035–10042.

- Javey, A.; Qi, P.; Wang, Q.; Dai, H. Ten-to 50-nm-Long Quasi-Ballistic Carbon Nanotube Devices Obtained without Complex Lithography. *Proc. Natl. Acad. Sci. U. S. A.* 2004, 101, 13408–13410.

- Wood, J. D.; Wells, S. A.; Jariwala, D.; Chen, K. S.; Cho, E.; Sangwan, V. K.; Liu, X.; Lauhon, L. J.; Marks, T. J.; Hersam, M. C. Effective Passivation of Exfoliated Black Phosphorus Transistors against Ambient Degradation. *Nano Lett.* **2014**, *14*, 6964–6970.

- 52. Xia, F.; Wang, H.; Jia, Y. Rediscovering Black Phosphorus as an Anisotropic Layered Material for Optoelectronics and Electronics. *Nat. Commun.* **2014**, *5*, 4458.

- Xia, F.; Perebeinos, V.; Lin, Y. M.; Wu, Y.; Avouris, P. The Origins and Limits of Metal-Graphene Junction Resistance. *Nat. Nanotechnol.* 2011, 6, 179–184.